#### **Features**

- Flexible analog signal generation and capture platform

- · Two daughter board slots

- Choose daughter boards from the 7 available types

- On-board high accuracy voltmeter

- On-board high performance clock source

- 1ppm clock stability / 0.5ps clock jitter

- Available for PXI and PXI Express

- LabView and LabWindows/CVI (VXIplug&play compatible) drivers included

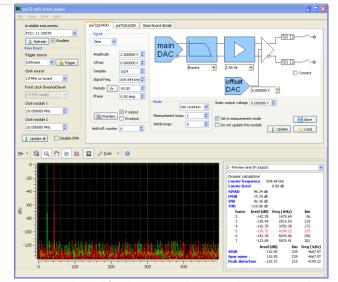

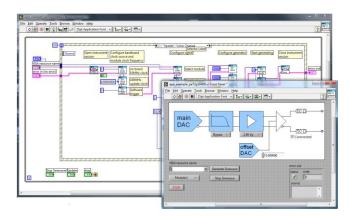

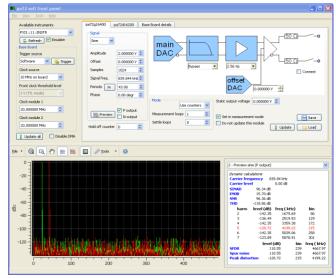

User control panel for the PA72 and an AWG daughter board

# General description

The PA72 platform is a platform of flexibility. It consists of a base board and one or two daughter boards. In daughter boards there is choice from several different generators, digitizers, filters, and Flexible Digital I/O modules. Also custom daughter boards can easily be created. This allows you to configure a data acquisition card exactly tailored to your needs.

The PA72 concept provides a flexible and cost effective solution for medium and high end analog functions.

Each daughter board is optimized for best signal performance. A PA72 daughter board typically has Differential In-/Outputs, Low THD, Low Noise and High Accuracy.

The base board contains a 2-channel high-stability and low-jitter PLL clock generator, trigger circuitry, and of course the PXI-bus interface. A digital voltmeter is available for self-calibration purposes (supported by the driver), and can also be used for custom development boards.

The base board is available with PXI bus interface (PA72) and PXI-Express bus interface (PA72e). Both baseboards accept the same daughter boards. The J2 connector is a small version (XJ4) to ensure both versions are hybrid-slot compatible.

### PA72 Base board

#### Description

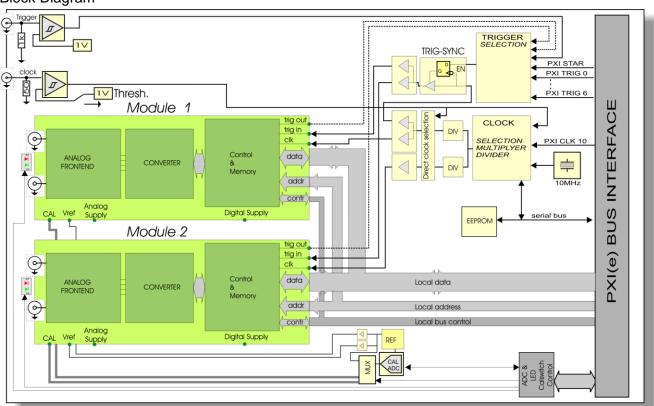

The PA72 base board contains a clock generator, trigger circuitry, a digital voltmeter and the PXI bus interface. In the block diagram below, the base board functions are yellow and the daughter board functions are green.

The clock generator is a low jitter PLL clock that has less than 0.5ps jitter for low loop filter bandwidths. With higher loop filter bandwidths, frequency settling time can be less than 250ms. The main clock frequency ranges from 2kHz up to 945MHz with a resolution of less than 1 kHz. Each daughter board slot has its own clock divider.

Therefore the clock for each daughter board can be different while maintaining proper synchronization. The PLL clock generator features a high stability, low noise and low jitter 10MHz on-board reference clock with 1ppm frequency stability. In addition the PLL can be locked to the PXI backplane clock or to an external reference clock. The on-board clock source can also be bypassed by an external direct clock.

The trigger input supports edge and level triggering and positive and negative going trigger signals. The trigger source can be software, PXI Star trigger, PXI Trigger 0-6, or external (front). Additionally, digitizer boards can be set to edge-trigger on the analog input signal.

#### **Block Diagram**

#### **Specifications**

#### PLL clock

Frequency range 2kHz to 945MHz Sync possibilities

10MHz backplane or 10MHz external clock PLL lock time 250ms - 1s (depending on loop filter BW) 0.5ps typical Jitter

**External clock input**

Clock rate DC to 500MHz

Threshold level 0V or 1V (programmable)

50 Ohm Input impedance

#### Front trigger input

Threshold level 1V 1k Ohm Input impedance -0.5V to +5.5V Max input level Coupling

#### **Trigger sources**

Digitizer's analog level trigger, Front trigger input, PXI STAR, PXI TRIG 0..6 (3..6 inverted), Software trigger

#### **Bus interface**

PA72 bus 32-bit PXI, burst mode support PA72e bus x1 PXI Express, burst mode support

Max. burst data rate 132 MByte/s

## PA72G16400 daughter board - 16-bit / 400Msps Arbitrary Waveform Generator

#### Description

The PA72G16400 is a 16-bit arbitrary waveform generator, capable of generating waveforms at speeds up to 400Msps. The high resolution and the high sample rate allows generating signals with very low quantization noise levels. An onboard offset voltage source allows generating offset signals while maintaining optimal utilization of the DAC's digital range. With the 8MWord of memory, there is lots of room for uploading several different patterns, allowing switching patterns with minimal bus communication.

#### Specifications

Channels 1 Resolution 16-bit

2kHz to 400MHz Update rate with PA72 clock Update rate external clock DC to 400MHz Pattern depth 8M-words

Output ranges Single-Ended  $0.32V_P$  to  $2.56V_P$  in 6 ranges Output ranges Differential 0.64V<sub>o</sub> to 5.12V<sub>o</sub> in 6 ranges DC-offset voltage -2.56 to +2.56V (>14-bit resolution) Output configuration 50-Ohm, Single-Ended or Differential Bandwidth DC to 80-140MHz

Bypass, 60MHz, 30MHz Output filters Absolute accuracy (Vout+)  $\pm$  (250 $\mu$ V + 0.1% of range +

0.1% of value) ±0.006% Relative accuracy

SNR (200Msps, 5V<sub>PP</sub> diff.) 69dB @ FOUT = 1MHz (BW 0-80MHz) 67dB @ FOUT = 10MHz (BW 0-80MHz) SNR (200Msps, 5V<sub>PP</sub> diff.)

THD (200Msps, 5V<sub>PP</sub> diff.) 84dB @ FOUT = 1MHz THD (200Msps, 5Vpp diff.) 73dB @ FOUT = 10MHz SFDR (200Msps, 5V<sub>PP</sub> diff.) 82dB @ FOUT = 1MHz

## PA72G14180 daughter board - 14-bit / 180Msps Arbitrary Waveform Generator

#### Description

The PA72G14180 is a 14-bit arbitrary waveform generator, capable of generating waveforms at speeds up to 180Msps. An onboard offset voltage source allows generating offset signals while maintaining optimal utilization of the DAC's digital range. With the 64MWord of memory, there is lots of room for uploading long complex waveforms. Also uploading of many different patterns is possible, allowing switching patterns with minimal bus communication.

#### Specifications

Channels Resolution 14-bit

Update rate with PA72 clock 2kHz to 180MHz DC to 180MHz Update rate with ext. clock Pattern depth 64M-words

**Output ranges**  $0.2V_P$  to  $3.28V_P$  proportional ranging

DC-offset voltage -2.56V to +2.56V

Output configuration 50-Ohm, Single-Ended or Differential

Bandwidth DC to 90MHz

Output filters Bypass, 30MHz, 15MHz

Absolute accuracy  $\pm$ (250 $\mu$ V + 0.1% of range + 0.1% of value)

Relative accuracy (INL) ±0.025% of range

SNR (180Msps,  $3.2V_{PP}$  diff.) 68dB @ F<sub>OUT</sub> = 1MHz (BW 0-70MHz) SNR (180Msps, 3.2V<sub>PP</sub> diff.) 64dB @ F<sub>OUT</sub> = 10MHz (BW 0-70MHz)

THD (180Msps, 2.0V<sub>PP</sub> diff.) 81dB @ F<sub>OUT</sub> = 1MHz 70dB @ F<sub>OUT</sub> = 10MHz THD (180Msps, 2.0V<sub>PP</sub> diff.) 82dB @ F<sub>OUT</sub> = 1MHz SFDR (180Msps, 2.0V<sub>PP</sub> diff.)

# PA72D16180A daughter board - 16-bit / 180Msps Digitizer

#### Description

The PA72D16180A is a 16-bit digitizer, capable of capturing waveforms at speeds up to 180Msps. An onboard offset voltage source allows capturing offset signals while still using the optimal range for maximum ADC utilization. Two onboard filters allow suppression of out-of-band noise. The 64MWord onboard memory enables capturing very long waveforms, or sequentially capturing multiple signals with minimal intermediate bus communication.

#### Specifications

Channels

Resolution 16-bit Sample rate 1MHz to 180MHz Memory depth 64M-words

Input configurations  $50\Omega$  or  $1M\Omega$ , AC or DC, Diff. or Single-

Ended

Input ranges 50Ω: 0.256V<sub>P</sub> to 3.072V<sub>P</sub> in 8 ranges  $1M\Omega$ :  $0.256V_P$  to  $15.36V_P$  in 12 ranges

DC-offset voltage 16-bit resolution

DC to 95-170MHz (typical, depending on Input bandwidth

Input filters Bypass, 60MHz, 30MHz

Absolute accuracy (Vin+)  $\pm$ (250 $\mu$ V + 0.1% of range + 0.2% of value)

Relative accuracy +0.006%

SNR (180Msps,  $50\Omega$ ,  $4V_{PP}$  diff) 69dB @  $F_{IN} = 1$ MHz (BW 0-80MHz) SNR (180Msps,  $50\Omega$ ,  $4V_{PP}$  diff) 67dB @  $F_{IN}$  = 10MHz (BW 0-80MHz)

THD (180Msps,  $50\Omega$ ,  $4V_{PP}$  diff) 85dB @  $F_{IN} = 1$ MHz THD (180Msps,  $50\Omega$ ,  $4V_{PP}$  diff) 81dB @  $F_{IN}$  = 10MHz SFDR(180Msps,  $50\Omega$ ,  $4V_{PP}$  diff)83dB @  $F_{IN}$  = 1MHz

### PA72D14130 daughter board - 14-bit / 130Msps Digitizer

#### Description

The PA72D14130 is a 14-bit digitizer, capable of capturing waveforms at speeds up to 130Msps. An onboard offset voltage source allows capturing offset signals while still using the optimal range for maximum ADC utilization. Two onboard filters allow suppression of out-of-band noise. The 64MWord onboard memory enables capturing very long waveforms, or sequentially capturing multiple signals with minimal intermediate bus communication.

#### **Specifications**

Channels 1

Resolution 14-bit

Sample rate 1MHz - 130MHz

Memory depth 64M-word

Input ranges (span) 0.338V<sub>P</sub> to 3.6V<sub>P</sub> in 8 ranges

Input operating area -3.6V to +3.6V

Input configuration Differential or Single-Ended Input impedance 10kOhm or 50-Ohm, DC or AC

DC-offset voltage -3.6V to +3.6V Input bandwidth 65MHz (typical) Input filters Bypass, 30MHz, 15MHz

Absolute accuracy  $\pm (250\mu V + 0.05\% \text{ of range } + 0.1\% \text{ of value})$

Relative accuracy (INL) ±0.025% of range

$\begin{array}{ll} \text{SNR (130Msps, 3.2V}_{\text{PP}} \text{ diff.)} & \text{66dB @ } F_{\text{IN}} = 1 \text{MHz (BW 0-60MHz)} \\ \text{SNR (130Msps, 3.2V}_{\text{PP}} \text{ diff.)} & \text{64dB @ } F_{\text{IN}} = 10 \text{MHz (BW 0-60MHz)} \\ \end{array}$

$\begin{array}{ll} \text{THD (130Msps, 3.2V}_{PP} \text{ diff.}) & \text{78dB @ } F_{\text{IN}} = 1 \text{MHz} \\ \text{THD (130Msps, 3.2V}_{PP} \text{ diff.}) & \text{74dB @ } F_{\text{IN}} = 10 \text{MHz} \\ \text{SFDR (130Msps, 3.2V}_{PP} \text{ diff.}) & \text{80dB @ } F_{\text{IN}} = 1 \text{MHz} \\ \end{array}$

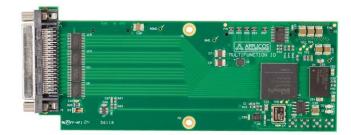

### PA72DIOS6016 daughter board – Multifunctional programmable Digital I/O

### Description

The PA72DIOS6016 is a multifunctional digital design core. The FPGA allows for implementing many different custom applications. The connector has 64 Input/Output pins which can be assigned as TTL I/O or as differential inputs. 128 MByte of DDR2 memory is available to the FPGA, and an onboard EEPROM allows for storing values in non-volatile memory. The I/O bank voltage can be FPGA-selected between 2.5 and 3.3 Volt.

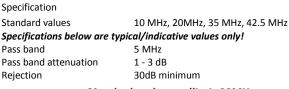

### Specification

FPGA Xilinx Spartan6 XC6SLX16

Logic cells 14579

CLB Flip-Flops 18224

Front connector VHDCI SCSI-5

Max. TTL/LVCMOS I/Os32Max. differential inputs32Max. differential outputs10

I/O voltages 2.5V and 3.3V

I/O configurations LVTTL, LVCMOS, PCI, SSTL, (B)LVDS\*,

LVPECL\*, and more.

DDR Memory size 1Gbit

DDR Memory frequency 800MHz

Total block RAM 576kBit

Block RAM max. frequency 320MHz

\* Differential signals as input only

# PA72DIOS6100 daughter board - Multifunctional programmable Digital I/O

#### Description

The PA72DIOS6100 is the larger equivalent of the PA72DIOS6016. It features a larger FPGA, and also allows differential output signals. The FPGA allows for implementing many different custom applications. The connector has 64 Input/Output pins which can be assigned as TTL or as differential pairs. 128 MByte of DDR2 memory is available to the FPGA, and an onboard EEPROM allows for storing values in non-volatile memory. The I/O bank voltage can be FPGA-selected between 1.2, 1.8, 2.5 and 3.3 Volt, allowing a wide range of electrical standards.

Specification

FPGA Xilinx Spartan6 XC6SLX100

Logic cells

101261

CLB Flip-Flops

126576

Front connector

VHDCI SCSI-5

Max. TTL/LVCMOS I/Os

32

Max. TTL/LVCMOS I/Os 32 Max. differential I/Os 32

I/O voltages 1.2V, 1.8V, 2.5V and 3.3V

I/O configurations LVTTL, LVCMOS, PCI, SSTL, (B)LVDS,

LVPECL, and more.

DDR Memory size 1Gbit

DDR Memory frequency 800MHz

Total block RAM 4824kBit

Block RAM max. frequency 320MHz

- This product information is preliminary -

## PA72BPF daughter board - Dual differential band pass filter

#### Description

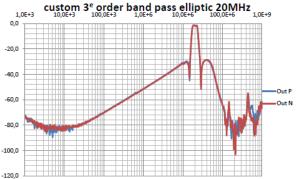

The PA72BPF daughter board is an additional filter board. It typically contains two selectable differential 3<sup>rd</sup> order elliptic band pass filters. These filter modules are tailored by Applicos to the customers' requirements. The filters can be used to filter the output signal of the generator daughter boards to achieve an even better distortion and noise suppression.

#### Software

The PA72 comes with a VXI*plug&play* compatible LabWindows/CVI driver, and a LabView driver. The driver API is fully documented, and gives you full control over the hardware. A LabView Application Example is included in the driver.

A Soft Front Panel tool is also included, which is a convenient way to quickly setup the hardware of your module and start a measurement.

## Ordering information:

#### PA72-nm / PA72e-nm

n = daughter board 1 (top position)

m = daughter board 2 (bottom position)

Daughter board codes:

0 = empty

1 = PA72G16400

2 = PA72G14180 5 = PA72D16180A

6 = PA72D14130

9 = PA72DIOS6016

A = PA72DIOS6100

F = PA72BPF Filter daughter board (specify filter requirements separately)

PA72-15  $\rightarrow$  PA72 base board with PXI-1 bus interface and a PA72G16400 generator on position 1 and a PA72D16180A digitizer on position 2 PA72e-20  $\rightarrow$  PA72e base board with PXI-Express bus interface and a PA72G14180 generator on position 1 and no board on position 2